We at Crack4sure are committed to giving students who are preparing for the ARM EN0-001 Exam the most current and reliable questions . To help people study, we've made some of our ARM Accredited Engineer exam materials available for free to everyone. You can take the Free EN0-001 Practice Test as many times as you want. The answers to the practice questions are given, and each answer is explained.

A Just-In-Time compiler writes instructions to a region of memory that is configured using a writeback cache strategy. For the locations that have been written, what is the MINIMUM cache maintenance that MUST be performed before the new instructions can be reliably executed?

In an ARMv7-A processor with Security Extensions, which of the following mechanisms best describes the way Secure memory is protected from access by software running in a Non-secure privileged mode?

What is the value of r0 after executing the following instruction sequence?

MOV r0, #200

MOV r5, #1

STR r3, [r0, r5, LSL#3]!

Under which of the following data-sharing scenarios would cache maintenance operations be necessary?

The Performance Monitoring Unit (PMU) of a Cortex-A9 processor permits direct measurement of which one of the following?

In which TWO of the following locations would a compiler typically place local variables? (Choose two)

The Cortex-A9 processor implements a feature called "small loop mode" which reduces power consumption when executing small loops by turning off instruction cache accesses. Which of the following statements describes a condition that must be satisfied for this mode to be enabled?

Which of the following is an accurate description of network storage as compared to on-chip RAM?

Capturing processor execution trace is characterized as being:

Which of the following will cause the ARM Compiler to target the Thumb instruction set?

Within the ARMv7 architecture, which one of the following features is unique to the ARMv7-A profile?

Which of the following register values would cause an unaligned access when the instruction LDRH r0, [r1] is executed?

A C code segment contains three calls to a function, foobar ().

This code segment is to be linked with a static library that defines foobar ().

Ignoring inlining, how many copies of foobar () will the ARM linker place in the output?

The automatic removal of a cache line from a cache to free the location is known as cache line:

Which TWO of the following interrupt types does a Generic Interrupt Controller (GIC) support? (Choose two)

Which of the following operations would count as intrusive to normal processor operation?

When using an Operating System, which of the following operations can NOT typically be done by user processes?

Why does Device memory prohibit speculative accesses?

Which one of the following statements best describes the function of vector catch logic?

Which of the following properties is a required characteristic of a Symmetric Multiprocessing (SMP) system?

Which of the following would enable the use of a symmetric multiprocessing (SMP) operating system?

Using a Generic Interrupt Controller (GIC), when the interrupt handler writes to the End of Interrupt Register (ICCEOIR), which of the following state transitions might occur for that interrupt ID?

If a Generic Interrupt Controller (GIC) implements 64 priority levels, which priority field bits hold the priority value?

A re-entrant interrupt handler would typically be used to:

What is the value of R2 after execution of the following instruction sequence?

MOV R3, #0xBA

MOV R2/#0x10

BIC R2, R3, R2

When applied to locations in memory configured using a write-back cache strategy, what does a data cache 'clean' operation do?

Cross compiling enables a programmer to:

When using the Performance Monitoring Unit to count runtime events the counter registers are limited to 32-bits. How can more than 2A32 events be counted without significantly impacting the software performance?

Which of the following statements is TRUE with respect to the power consumption related to memory accesses?

In which of the following situations would you use a mutex to avoid synchronization problems?

A deeply embedded real-time industrial control system is missing some hard real-time interrupt deadlines. Which of the following performance analysis techniques is the most suitable for identifying which routines are causing the problem?

Assume a Big-Endian (BE) memory system with the following memory contents.

Byte Address Contents

0x100 0x11

0x101 0x22

0x102 0x33

0x103 0x44

If R5 = 0x100, what are the contents of R4 after performing the following operation?

LDR R4, [R5]

Which one of these statements is TRUE about code running on final hardware without a debugger attached?

A simple method of measuring the performance of an application is to record the execution time using the clock on the wall or a wristwatch.

When is this method INAPPROPRIATE?

The following C function is compiled with hard floating point linkage.

float function(int a, float b, int c, float d);

Which register is used to pass argument c?

Which of the following features was added in version 2 of the ARM Architecture Advanced SIMD extensions?

Which of the following functions can be performed by a spinlock?

Many ARM cores provide two instruction sets, ARM and Thumb. Which THREE of the following statements apply to the Thumb instruction set implemented for the ARMv7-A architecture? (Choose three)

The following ARM instruction can be used to return from an exception:

movs pc, lr

Apart from the program counter, which register is updated by this instruction?

To return from a Data Abort handler and re-execute the aborting instruction, what value should be loaded to the PC?

Which of the following is a REQUIRED feature in the ARMv7 architecture?

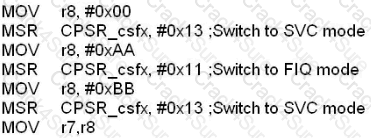

Consider the following piece of code:

The value of r7 after execution of the above piece of code is:

The purpose of a translation lookaside buffer (TLB) is to:

In the Generic Interrupt Controller (GIC), when an interrupt is requested, but is not yet being handled, it is in which of the following states?

Which of the following processors includes a Generic Interrupt Controller as a standard component?

In an ARMv7-A processor, with which level of the memory system is the Memory Management Unit (MMU) associated?

Implementing loops using a decrementing counter which exits the loop when a counter reaches zero can be beneficial for power and performance. This is because:

When debugging an embedded Linux system, which one of the following techniques can be used to halt a single user thread, while allowing other threads to continue to run during the debug process?

A program running on a development board that is connected to a host using a debugger can access a file on the host by using:

Which of the following is an external exception?

An undefined instruction will cause an Undefined Instruction exception to be taken when:

Processors which implement the ARMv7-A architecture can be configured to allow unaligned memory access. Unaligned accesses have a number of advantages, disadvantages, and limitations.

Which TWO of the following statements are true? (Choose two)

In which of the following scenarios would cache maintenance operations be necessary in an ARMv7 system?

A Programmer's View CPU model usually provides:

When setting the initial location of the stack pointer and the base address of the heap, the ARM EABI requires that the:

A 32KB 4-way set associative instruction cache supports a cache line size of 64 bytes. How many bits are required to index a cache line in a way?

An Advanced SIMD intrinsic has the prototype:

int16x4_t vmul_n_s16(int16x4_t a, int16_t b);

How many multiplications does this intrinsic compute?

The size of a C 'int' type in the ARM architecture is:

3 Months Free Update

3 Months Free Update

3 Months Free Update